# VSM's

# Somashekhar R Kothiwale Institute of Technology, Nipani-591237

# DEPARTMENT OF ELECTRONICS &

# **COMMUNICATION ENGG**

# **VLSI LAB**

# 15ECL77

## BY

## PROF. CHETAN ALATAGI

## EXPT.NO.1

**TITLE :** Write Verilog Code for the inverter circuit and their Test Bench for verification, observe the waveform and synthesize the code with technological library with given Constraints. Do the initial timing verification with gate level simulation.

#### TOOL REQUIRED: XILINX 10.2

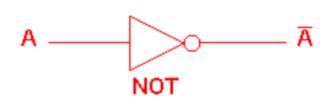

**THEORY :** The NOT gate or an inverter is an electronic circuit that produces an inverted version of the input at its output. It is also known as an inverter. If the input variable is A, the inverted output is known as NOT A. This is also shown as A', or A with a bar over the top, as shown at the outputs. The diagrams below show two ways that the NAND logic gate can be configured to produce a NOT gate. It can also be done using NOR logic gates in the same way.

Symbol

| Truth Table |

|-------------|

|-------------|

| NOT Gate |        |  |

|----------|--------|--|

| INPUT    | OUTPUT |  |

| А        | A'     |  |

| 0        | 1      |  |

| 1        | 0      |  |

#### Verilog Code For Inverter:

module inv(a,b); input a; output b; assign  $b = \sim(a)$ ; endmodule

#### Test Bench:

module inv\_test; reg a; wire b; inv uut ( .a(a), .b(b) ); initial begin a = 0; #100; a = 0; #100;a = 0; #100;

```

a = 1; #100;

end

endmodule

```

**RESULT:** Verilog code for the inverter circuit and its test bench for verification is written, the waveform is observed and the code is synthesized with the technological library and is verified.

## EXPT.NO.2

**TITLE:** Write Verilog Code for the buffer circuit and their Test Bench for verification, observe the waveform and synthesize the code with technological library with given Constraints. Do the initial timing verification with gate level simulation.

#### TOOL REQUIRED: XILINX 10.2

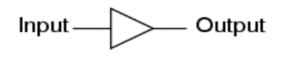

**THEORY:** A special logic gate called a buffer is manufactured to perform the same function as two inverters. Its symbol is simply a triangle, with no inverting "bubble" on the output terminal. Buffer gates merely serve the purpose of signal amplification: taking a "weak" signal source that isn't capable of sourcing or sinking much current, and boosting the current capacity of the signal so as to be able to drive a load.

Symbol

**Truth Table**

| BUFFER       |   |

|--------------|---|

| INPUT OUTPUT |   |

| 0            | 0 |

| 1            | 1 |

#### Verilog Code For Buffer

module buffer (a,b); input a; output b; assign b = (a); endmodule

#### Test Bench:

module buffer\_test;

reg a; wire b; buffer uut ( .a(a), .b(b) );

initial begin a = 0; #100; a = 1; #100; a = 0; #100; a = 1; #100;

end endmodule **RESULT:** Verilog code for the buffer circuit and its test bench for verification is written, the waveform is observed and the code is synthesized with the technological library and is verified.

## EXPT.NO.3

**TITLE :** Write Verilog Code for the transmission circuit and their Test Bench for verification, observe the waveform and synthesize the code with technological library with given Constraints. Do the initial timing verification with gate level simulation.

#### TOOL REQUIRED: XILINX 10.2

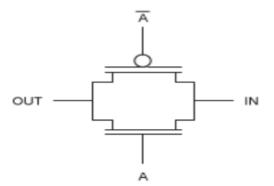

**THEORY:** A transmission gate, or analog switch, is defined as an electronic element that will selectively block or pass a signal level from the input to the output. Basic Operation This solidstate switch is comprised of a pMOS transistor and nMOS transistor. The control gates are biased in a complementary manner so that both transistors are either on or off. When the voltage on node A is a Logic 1, the complementary Logic 0 is applied to node active-low A, allowing both transistors to conduct and pass the signal at IN to OUT. When the voltage on node active-low A is a Logic 0, the complementary Logic 1 is applied to node A, turning both transistors off and forcing a high-impedance condition on both the IN and OUT nodes. This high-impedance condition represents the third "state" (high, low, or high-Z) that the channel may reflect downstream. The schematic diagram (Figure 1) includes the arbitrary labels for IN and OUT, as the circuit will operate in an identical manner if those labels were reversed. This design provides true bidirectional connectivity without degradation of the input signal. Figure 1. Schematic representation of a transmission gate.

#### Symbol

#### Truth Table

| А | IN      | OUT        |

|---|---------|------------|

| Н | Н       | Н          |

| Н | L       | L          |

| L | X(don't | Z(high     |

|   | care)   | impedance) |

#### 3. Verilog Code For Transmission

module trans(a,b,an); input a,en; output b;

reg b; always @(a,en) begin if(en == a'b1) b=a; else b=1'bz; end endmodule

#### **Test Bench:**

module trans\_test;

reg a; reg en; wire b; trans uut ( .a(a), .b(b), .en(en) );

initial begin

| en = 1; | a=1 | ; | #100; |

|---------|-----|---|-------|

| en = 1; | a=0 | ; | #100; |

| en = 0; | a=1 | ; | #100; |

| en = 0; | a=1 | ; | #100; |

|         |     |   |       |

end endmodule

**RESULT:** Verilog code for the transmission gate circuit and its test bench for verification is written, the waveform is observed and the code is synthesized with the technological library and is verified

**TITLE :** Write Verilog Code for the Basic/Universal gates and their Test Bench for verification, observe the waveform and synthesize the code with technological library with given Constraints. Do the initial timing verification with gate level simulation.

#### TOOL REQUIRED: XILINX 10.2

**THEORY:** Digital systems are said to be constructed by using logic gates. These gates are the AND, OR, NOT, NAND, NOR, EXOR and EXNOR gates. The basic operations are described below with the aid of truth tables.

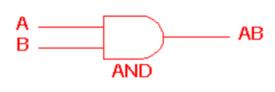

Symbol

**Truth Table**

| INPUT |   | OUTPUT |

|-------|---|--------|

| Α     | В | AB     |

| 0     | 0 | 0      |

| 0     | 1 | 0      |

| 1     | 0 | 0      |

| 1     | 1 | 1      |

The AND gate is an electronic circuit that gives a high output (1) only if all its inputs are high. A dot (.) is used to show the AND operation i.e. A.B. Bear in mind that this dot is sometimes omitted i.e. AB

A A+B

| INPUT |   | OUTPUT |

|-------|---|--------|

| Α     | В | AB     |

| 0     | 0 | 0      |

| 0     | 1 | 1      |

| 1     | 0 | 1      |

| 1     | 1 | 1      |

The OR gate is an electronic circuit that gives a high output (1) if one or more of its inputs are high. A plus (+) is used to show the OR operation.

Symbol

Truth Table

| INPUT | OUTPUT |  |

|-------|--------|--|

| Α     | Α'     |  |

| 0     | 1      |  |

| 1     | 0      |  |

The NOT gate is an electronic circuit that produces an inverted version of the input at its output. It is also known as an inverter. If the input variable is A, the inverted output is known as NOT A. This is also shown as A', or A with a bar over the top, as shown at the outputs. The diagrams below show two ways that the NAND logic gate can be configured to produce a NOT gate. It can also be done using NOR logic gates in the same way.

Symbol

| INPUT |   | OUTPUT  |

|-------|---|---------|

| Α     | В | A XOR B |

| 0     | 0 | 0       |

| 0     | 1 | 1       |

| 1     | 0 | 1       |

| 1     | 1 | 0       |

**Truth Table**

The 'Exclusive-OR' gate is a circuit which will give a high output if either, but not both, of its two inputs are high. An encircled plus sign () is used to show the EOR operation.

ENOR

| INPUT |   | OUTPUT  |

|-------|---|---------|

| Α     | В | A XOR B |

| 0     | 0 | 1       |

| 0     | 1 | 0       |

| 1     | 0 | 0       |

| 1     | 1 | 1       |

The 'Exclusive-NOR' gate circuit does the opposite to the EOR gate. It will give a low output if either, but not both, of its two inputs are high. The symbol is an EXOR gate with a small circle on the output. The small circle represents inversion.

Symbol

| Truth | Table |

|-------|-------|

|-------|-------|

| INP | TUT     | OUTPUT |

|-----|---------|--------|

|     | A XOR B |        |

| 0   | 0       | 0      |

| 0   | 1       | 1      |

| 1   | 0       | 1      |

| 1   | 1       | 1      |

9

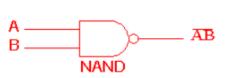

This is a NOT-AND gate which is equal to an AND gate followed by a NOT gate. The outputs of all NAND gates are high if any of the inputs are low. The symbol is an AND gate with a small circle on the output. The small circle represents inversion.

Symbol

| INP | TUT | OUTPUT  |

|-----|-----|---------|

| Α   | В   | A XOR B |

| 0   | 0   | 1       |

| 0   | 1   | 0       |

| 1   | 0   | 0       |

| 1   | 1   | 0       |

**Truth Table**

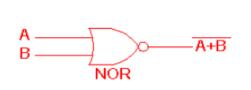

This is a NOT-OR gate which is equal to an OR gate followed by a NOT gate. The outputs of all NOR gates are low if any of the inputs are high. The symbol is an OR gate with a small circle on the output. The small circle represents inversion.

#### Verilog Code For Universal Gates

```

module uni(a,b,z1,z2,z3,z4,z5,z6);

input a,b;

output z1,z2,z3,z4,z5,z6;

assign z1 = a\&b;

assign z^2 = a | b;

assign z3 = \sim (a\&b);

assign z4 = \langle a | b \rangle;

assign z5 = a^b;

assign z6 = (a^b);

endmodule

Test Bench:

module uni_test;

reg a; reg b;

wire z1:

wire z2;

wire z3;

wire z4:

wire z5;

wire z6;

uni uut (

.a(a), .b(b),

.z1(z1), .z2(z2),.z3(z3),

.z4(z4), .z5(z5),.z6(z6)

);

initial begin

a = 0;b = 0;#100;

a = 0;b = 1;\#100;

a = 1;b = 0;\#100;

a = 1;b = 1;\#100;

end

```

endmodule

**RESULT:** Verilog code for the basic/universalgates circuit and its test bench for verification is written, the waveform is observed and the code is synthesized with the technological library and is verified.

## EXPT.NO.5 a

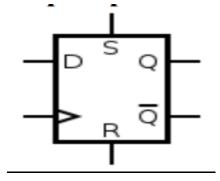

TITLE: Write Verilog Code for the SR Flip Flop and their Test Bench for verification, observe the waveform and synthesize the code with technological library with given Constraints. Do the initial timing verification with gate level simulation.

#### TOOL REQUIRED: XILINX 10.2

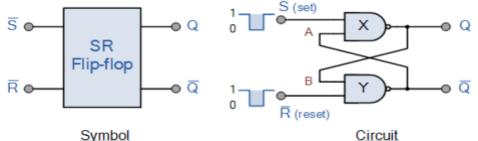

THEORY: It can be seen that when both inputs S = "1" and R = "1" the outputs Q and Q can be at either logic level "1" or "0", depending upon the state of the inputs S or R BEFORE this input condition existed. Therefore the condition of S = R = "1" does not change the state of the outputs Q and Q. VLSI Lab However, the input state of S = "0" and R = "0" is an undesirable or invalid condition and must be avoided. The condition of S = R = "0" causes both outputs Q and Q to be HIGH together at logic level "1" when we would normally want Q to be the inverse of Q. The result is that the flip-flop looses control of Q and Q, and if the two inputs are now switched "HIGH" again after this condition to logic "1", the flip-flop becomes unstable and switches to an unknown data state based upon the unbalance as shown in the following switching diagram.

| S   | m | ho | L |

|-----|---|----|---|

| - 3 |   | 00 | L |

|     |   |    |   |

| Ing | out | Out | tput | Description |

|-----|-----|-----|------|-------------|

| S   | R   | Q   | Q    |             |

| 0   | 0   | 0   | 0    | Memory no   |

| 0   | 0   | 0   | 1    | change      |

| 0   | 1   | 1   | 0    | Reset       |

| 0   | 1   | 0   | 0    |             |

| 1   | 0   | 0   | 1    | Set         |

| 1   | 0   | 1   | 1    |             |

| 1   | 1   | 0   | Z    | Invalid     |

| 1   | 1   | 1   | Z    | Condition   |

Truth Table

#### Verilog Code For SR Flip-Flop

module srff( sr, reset, clk,q, qbar ); input [0:1]sr; input reset, clk;

```

output q, qbar;

reg q, qbar;

always @( sr , reset, posedge clk )

begin

if (reset == 0)

begin

q = 1'b0;

qbar=1'b1;

end

else

begin

case(sr)

2'b00:begin q=q;qbar=qbar;end

2'b01:begin q=1'b0;qbar=1'b1;end

2'b10:begin q=1'b1;qbar=1'b0;end

2'b11:begin q=1'bz;qbar=1'bz;end

endcase

end

end

endmodule

```

#### Test Bench:

module srff\_test; reg [0:1] sr;reg reset; reg clk; wire q; wire qbar; srff uut (.sr(sr), .reset(reset), .clk(clk), .q(q), .qbar(qbar) ); initial clk =1'b0; always #10 clk=~clk; initial begin reset=0; #100; reset=1: sr = 00; #100;sr = 01; #100;sr = 10; #100;sr = 11;#100;

#### end

```

endmodule

```

**RESULT:** Verilog code for the SR Flip Flop circuit and its test bench for verification is written, the waveform is observed and the code is synthesized with the technological library and is verified

## EXPT.NO.5 b

**TITLE :** Write Verilog Code for the D Flip Flop and their Test Bench for verification, observe the waveform and synthesize the code with technological library with given Constraints. Do the initial timing verification with gate level simulation.

#### TOOL REQUIRED: XILINX 10.2

**THEORY:** In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are fundamental building blocks of digital electronics systems used in computers, communications, and many other types of systems. Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a "one" and the other represents a "zero". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. D flip-flop The D flip-flop is widely used. It is also known as a "data" or "delay" flip-flop. The D flip-flop captures the value of the D-input at a definite portion of the clock cycle (such as the rising edge of the clock). That captured value becomes the Q output. At other times, the output Q does not change. The D flip-flop can be viewed as a memory cell, a zero-order hold, or a delay line. D flip-flop symbol

#### Verilog Code For D Flip-Flop

module dff( d, reset, clk,q, qbar ); input d ; input reset, clk ; output q, qbar ; reg q, qbar ;

```

always @( reset, posedge clk )

begin

if ( reset == 0 )

begin

q = 1'b0;

qbar=1'b1;

end

else

begin

q = 1'b0;

qbar = 1'b1;

end

end

end

endmodule

```

#### **Test Bench:**

```

module dff_test;

reg d; reg reset; reg clk;

wire q; wire qbar;

dff uut (.d(d), .reset(reset),.clk(clk),

.q(q), .qbar(qbar) );

```

initial

clk =1'b0; always #10 clk=~clk;

initial begin reset=0; #100; reset=1; d=1'b0; #100; d=1'b1; #100; end endmodule

**RESULT:** Verilog code for the D Flip Flop circuit and its test bench for verification is written, the waveform is observed and the code is synthesized with the technological library and is verified.

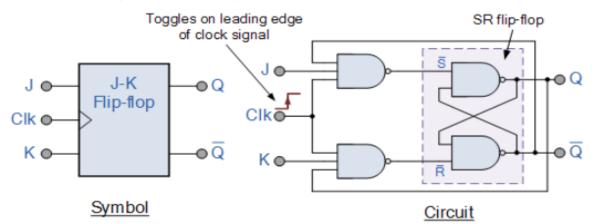

## EXPT.NO.5 c

**TITLE :** Write Verilog Code for the SR Flip Flop and their Test Bench for **verification**, observe the waveform and **synthesize** the code with technological library with given Constraints. Do the initial timing verification with gate level simulation.

#### TOOL REQUIRED: XILINX 10.2

**THEORY:** Then the JK flip-flop is basically an SR flip flop with feedback which enables only one of its two input terminals, either SET or RESET to be active at any one time thereby eliminating the invalid condition seen previously in the SR flip flop circuit. Also when both the J and the K inputs are at logic level "1" at the same time, and the clock input is pulsed either "HIGH", the circuit will "toggle" from its SET state to a RESET state, or visa-versa. This results in the JK flip flop acting more like a T-type toggle flip-flop when both terminals are "HIGH". Although this circuit is an improvement on the clocked SR flip-flop it still suffers from timing problems called "race" if the output Q changes state before the timing pulse of the clock input has time to go "OFF". To avoid this the timing pulse period (T) must be kept as short as possible (high frequency). As this is sometimes not possible with modern TTL IC's the much improved MasterSlave JK Flip-flop was developed.

#### Truth Table:

| Input         K         Q           J         K         Q           0         0         0           0         0         0           0         1         1 | Out | tput | Description |                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------------|---------------------|

| J                                                                                                                                                         | K   | Q    | Q           |                     |

| 0                                                                                                                                                         | 0   | 0    | 0           | Memory no<br>change |

| 0                                                                                                                                                         | 0   | 0    | 1           | change              |

| 0                                                                                                                                                         | 1   | 1    | 0           | Reset               |

| 0                                                                                                                                                         | 1   | 0    | 0           |                     |

| 1                                                                                                                                                         | 0   | 0    | 1           | Set                 |

| 1                                                                                                                                                         | 0   | 1    | 1           |                     |

| 1                                                                                                                                                         | 1   | 0    | 1           | Toggle              |

| 1                                                                                                                                                         | 1   | 1    | 0           |                     |

#### Verilog Code For JK Flip-Flop

```

module jkff( jk, reset, clk,q, qbar );

input [0:1]jk;

input reset, clk;

output q, qbar;

reg q, qbar ;

always @(jk, reset, posedge clk)

begin

if (reset == 0)

begin

q = 1'b0;

qbar=1'b1;

end

else

begin

case(jk)

2'b00:begin q=q;qbar=qbar;end

2'b01:begin q=1'b0;qbar=1'b1;end

2'b10:begin q=1'b1;qbar=1'b0;end

2'b11:begin q=~q;qbar=~qbar;end

endcase

end

end

endmodule

```

#### **Test Bench :**

```

module jkff_test;

reg [0:1] jk;reg reset;reg clk;

wire q;wire qbar;

jkff uut (.jk(jk),.reset(reset),.clk(clk),

.q(q), .qbar(qbar));

initial

clk =1'b0;

always #10 clk=~clk;

initial begin

reset=0;

#100;

reset=1;

jk=00; #100;

jk=01; #100;

jk=10; #100;

jk=11; #100;

end

endmodule

```

**RESULT:** Verilog code for the JK Flip Flop circuit and its test bench for verification is written, the waveform is observed and the code is synthesized with the technological library and is verified.

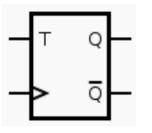

## EXPT.NO.5 d

**TITLE :** Write Verilog Code for the SR Flip Flop and their Test Bench for **verification**, observe the waveform and **synthesize** the code with technological library with given Constraints. Do the initial timing verification with gate level simulation.

#### TOOL REQUIRED: XILINX 10.2

**THEORY:** When T is held high, the toggle flip-flop divides the clock frequency by two; that is, if clock frequency is 4 MHz, the output frequency obtained from the flip-flop will be 2 MHz. This "divide by" feature has application in various types of digital counters. A T flip-flop can also be built using a JK flip-flop (J & K pins are connected together and act as T) or a D flip-flop (T input XOR Qprevious drives the D input).

#### **Truth Table**

| Input | Ou | tput | Description         |

|-------|----|------|---------------------|

| Т     | Q  | Q    |                     |

| 0     | 0  | 0    | Memory no           |

| 0     | 1  | 1    | Memory no<br>change |

| 1     | 0  | 1    | Toggle              |

| 1     | 1  | 0    |                     |

#### Verilog Code For T Flip-Flop

```

module tff( t, reset, clk,q, qbar );

input t;

input reset, clk;

output q, qbar ;

reg q, qbar;

always @(t, reset, posedge clk)

begin

if (reset == 0)

begin

q = 1'b0;

qbar=1'b1;

end

else

begin

case(t)

1'b0: begin q=q; qbar=qbar; end

1'b1: begin q=qbar; qbar=~qbar; end

endcase

end

```

end endmodule

#### **Test Bench:**

```

module tff_test;

reg t;reg reset;reg clk;

wire q;wire qbar;

tff uut (.t(t),.reset(reset),.clk(clk),

.q(q),.qbar(qbar));

initial

clk =1'b0;

always #10 clk=~clk;

initial begin

#100;

reset=0;

reset=1;

t=1'b0; #100;

t=1'b1; #100;

end

endmodule

```

```

RESULT: Verilog code for the T Flip Flop circuit and its test bench for verification is written, the waveform is observed and the code is synthesized with the technological library and is verified.

```

## EXPT.NO.6 a

**TITLE :** Write Verilog Code for the Serial adder circuit and their Test Bench for verification, observe the waveform and synthesize the code with technological library with given Constraints. Do the initial timing verification with gate level simulation.

#### TOOL REQUIRED: XILINX 10.2

**THEORY:** The serial binary adder or bit-serial adder is a digital circuit that performs binary addition bit by bit. The serial full adder has three single-bit inputs for the numbers to be added and the carry in. There are two single-bit outputs for the sum and carry out. The carry-in signal is the previously calculated carry-out signal. The addition is performed by adding each bit, lowest to highest, one per clock cycle. Serial binary addition is done by a flip-flop and a full adder. The flip-flop takes the carry-out signal on each clock cycle and provides its value as the carry-in signal on the next clock cycle. After all of the bits of the input operands have arrived, all of the bits of the sum have come out of the sum output.

#### Verilog Code For Serial Adder

```

module serial_adder(a,b,sum,cout);

input [3:0] a,b;

output cout;

output [3:0] sum;

reg [3:0] sum;

reg cout;

reg [4:0] carry;

integer i;

always @(a,b)

begin

carry[0]=0;

for(i=0;i<=3;i=i+1)

begin

sum[i] = a[i] \wedge b[i] \wedge carry[i];

carry [i+1] = ( a[i] & b[i] ) | (b[i] & carry[i]) | (carry[i] & a[i] ) ;

end

cout = carry[4];

end

endmodule

```

#### **Test Bench:**

module serial\_adder\_test; reg [3:0] a;reg [3:0] b;

```

wire [3:0] sum;wire cout;

serial_adder uut (.a(a),.b(b),

.sum(sum),.cout(cout) );

initial begin

a = 0101;b = 1101; #100;

a = 0111;b = 1001; #100;

a = 1011;b = 0001; #100;

a = 0001;b = 1100; #100;

end

```

#### endmodule

**RESULT:** Verilog code for the serial adder circuit and its test bench for verification is written, the waveform is observed and the code is synthesized with the technological library and is verified.

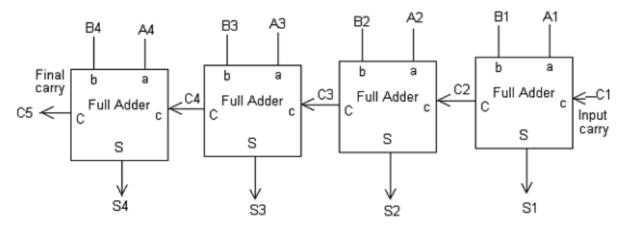

## EXPT.NO.6 b

**TITLE :** Write Verilog Code for the parallel adder circuit and their Test Bench for verification, observe the waveform and synthesize the code with technological library with given Constraints. Do the initial timing verification with gate level simulation.

#### TOOL REQUIRED: XILINX 10.2

**THEORY:** Addition is a fundamental operation for any digital system, digital signal processing or control system. A fast and accurate operation of a digital system is greatly influenced by the performance of the resident adders. Adders are also very important component in digital systems because of their extensive use in other basic digital operations such as subtraction, multiplication and division Parallel adder is a combinatorial circuit (not clocked, does not have any memory and feedback) adding every bit position of the operands in the same time. Thus it is requiring number of bit-adders(full adders + 1 half adder) equal to the number of bits to be added. The Parallel adder is constructed by cascading full adders (FA) blocks in series. One full adder is responsible for the addition of two binary digits at any stage of the ripple carry. The carryout of one stage is fed directly to the carry-in of the next stage.

#### 6. b) Verilog Code For Parallel Adder

module parallel ( a, b, cin, sum, cout ); input [3:0] a, b ; input cin ; output [3:0] sum; output cout; wire [3:0] c; fa stage0 ( a[0], b[0], cin, sum[0], c[0] ) ; fa stage1 ( a[1], b[1], c[0], sum[1], c[1] ) ;

```

fa stage2 ( a[2], b[2], c[1], sum[2], c[2] ) ;

fa stage3 ( a[3], b[3], c[2], sum[3], c[3] ) ;

assign cout = c[3] ;

endmodule

```

## **Component Code**

module fa( a, b, cin, s, cout ) ; input a, b, cin; output s, cout; assign s =  $a \wedge b \wedge cin$ ; assign cout = ( a & b ) | ( b & cin ) | ( cin & a ) ; endmodule

## Test Bench:

```

module parallel_test;

reg [3:0] a;reg [3:0] b;reg cin;

wire [3:0] sum;wire cout;

parallel uut (

.a(a),.b(b),.cin(cin),

.sum(sum),.cout(cout)

);

initial begin

a = 0101;b = 1101; cin=0;#100;

a = 0111;b = 1001; cin=0;#100;

a = 1011;b = 0001; cin=0;#100;

a = 0001;b = 1100; cin=0;#100;

end

endmodule

```

**RESULT:** Verilog code for the parallel adder circuit and its test bench for verification is written, the waveform is observed and the code is synthesized with the technological library and is verified.

## EXPT.NO.7 a

**TITLE :** Write Verilog Code for the synchronous counter circuit and their Test Bench for verification, observe the waveform and synthesize the code with technological library with given Constraints. Do the initial timing verification with gate level simulation.

#### TOOL REQUIRED: XILINX 10.2

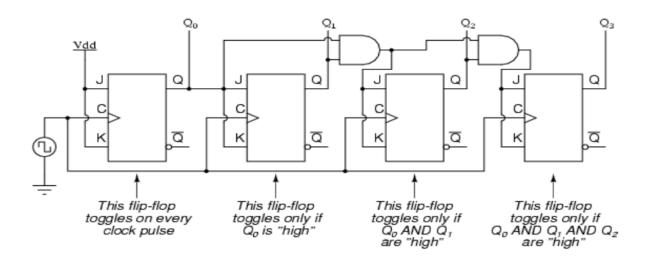

**THEORY:** A synchronous counter, in contrast to an asynchronous counter, is one whose output bits change state simultaneously, with no ripple. The only way we can build such a counter circuit from J-K flip-flops is to connect all the clock inputs together, so that each and every flip-flop receives the exact same clock pulse at the exact same time. The figure shows a four-bit synchronous "up" counter. Each of the higher-order flip-flops are made ready to toggle (both J and K inputs "high") if the Q outputs of all previous flip-flops are "high." Otherwise, the J and K inputs for that flip-flop will both be "low," placing it into the "latch" mode where it will maintain its present output state at the next clock pulse. Since the first (LSB) flip-flop needs to toggle at every clock pulse, its J and K inputs are connected to Vcc or Vdd, where they will be "high" all the time. The next flip-flop need only "recognize" that the first flip-flop's Q output is high to be made ready to toggle, so no AND gate is needed. However, the remaining flip-flops should be made ready to toggle only when all lower-order output bits are "high," thus the need for AND gates.

#### I) Verilog Code For Synchronous Down Counter

module sync ( clk, q, qbar ) ; input clk ; output [3:0] q ; output [3:0] qbar ;

```

wire [1:0] s;

supply1 vdd ;

jkff c0 ( vdd, vdd, clk , q[0], qbar [0] ) ;

jkff c1 (qbar [0], qbar [0], clk , q[1], qbar [1] ) ;

assign s[0]= qbar[0] & qbar[1];

jkff c2 (s[0],s[0], clk ,q[2], qbar [2] ) ;

assign s[1]= qbar[0] & qbar[1] & qbar[2] ;

jkff c3 (s[1], s[1], clk , q[3], qbar [3] ) ;

endmodule

```

#### **Component Code**

module jkff ( j, k ,clk, qx, qxbar ) ; input clk , j , k ; output qx, qxbar ; reg qx, qxbar ; initial begin qx = 1'b0 ; qxbar = 1'b1 ; end always @ (posedge clk ) begin qx = (j & (~qx)) | ((~k) & qx); qxbar = ~qx ; end endmodule

#### Test Bench :

```

module sync_test;

reg clk;

wire [3:0] q;wire [3:0] qbar;

async uut (.clk(clk),

.q(q),.qbar(qbar) );

```

initial clk =1'b0; always #10 clk=~clk; endmodule

#### II) Verilog Code For Synchronous Down Counter

```

module sync ( clk, q, qbar ) ;

input clk ;

output [3:0] q ;

output [3:0] qbar ;

```

```

wire [1:0] s;

supply1 vdd ;

jkff c0 ( vdd, vdd, clk , q[0], qbar [0] ) ;

jkff c1 (q [0], q [0], clk , q[1], qbar [1] ) ;

assign s[0]= q[0] & q[1];

jkff c2 (s[0],s[0], clk ,q[2], qbar [2] ) ;

assign s[1]= q[0] & q[1] & q[2] ;

jkff c3 (s[1], s[1], clk , q[3], qbar [3] ) ;

endmodule

```

## **Component Code**

```

module jkff ( j, k ,clk, qx, qxbar ) ;

input clk , j , k ;

output qx, qxbar ;

reg qx, qxbar ;

initial

begin

qx = 1'b0 ;

qxbar = 1'b1 ;

end

always @ ( posedge clk )

begin

qx = ( j & ( ~ qx ) ) | ( ( ~ k ) & qx ) ;

qxbar = ~ qx ;

end

endmodule

```

#### **Test Bench :**

```

module sync_test;

reg clk;

wire [3:0] q;wire [3:0] qbar;

async uut (.clk(clk),

.q(q),.qbar(qbar));

initial

clk =1'b0;

always #10 clk=~clk;

endmodule

```

**RESULT:** Verilog code for the synchronous counter circuit and its test bench for verification is written, the waveform is observed and the code is synthesized with the technological library and is verified.

## EXPT.NO.7 b

**TITLE :** Write Verilog Code for the asynchronous counter circuit and their Test Bench for verification, observe the waveform and synthesize the code with technological library with given Constraints. Do the initial timing verification with gate level simulation.

#### TOOL REQUIRED: XILINX 10.2

**THEORY:** Asynchronous counters are those whose output is free from the clock signal. Because the flip flops in asynchronous counters are supplied with different clock signals, there may be delay in producing output. The required number of logic gates to design asynchronous counters is very less. So they are simple in design. Another name for Asynchronous counters is "Ripple counters". The number of flip flops used in a ripple counter is depends up on the number of states of counter (ex: Mod 4, Mod 2 etc). The number of output states of counter is called "Modulus" or "MOD" of the counter. The maximum number of states that a counter can have is 2n where n represents the number of flip flops used in counter. For example, if we have 2 flip flops, the maximum number of outputs of the counter" or "MOD-4 counter".

#### I) Verilog Code For Asynchronous Down Counter

module async ( clk, q, qbar ); input clk ; output [3:0] q ; output [3:0] qbar; supply1 vdd; jkff c0 (vdd, vdd, clk, q[0], qbar [0]); jkff c1 (vdd, vdd, q[0], q[1], qbar [1]); jkff c2 (vdd, vdd, q[1], q[2], qbar [2]); jkff c3 (vdd, vdd, q[2], q[3], qbar [3]); endmodule **Component Code** module jkff ( j, k ,clk, qx, qxbar ) ; input clk, j, k; output qx, qxbar; reg qx, qxbar; initial begin qx = 1'b0;qxbar = 1'b1;end always @ (posedge clk) begin qx = (j&(~qx)) | ((~k)&qx);

```

qxbar = ~ qx ;

end

endmodule

```

#### **Test Bench :**

```

module sync_test;

reg clk;

wire [3:0] q;wire [3:0] qbar;

async uut (

.clk(clk),

.q(q),.qbar(qbar)

);

```

```

initial

clk =1'b0;

always #10 clk=~clk;

endmodule

```

#### II) Verilog Code For Asynchronous Up Counter

```

module async ( clk, q, qbar ) ;

input clk ;

output [3:0] q ;

output [3:0] qbar ;

supply1 vdd ;

jkff c0 ( vdd, vdd, clk , q[0], qbar [0] ) ;

jkff c1 (vdd, vdd, qbar[0] , q[1], qbar [1] ) ;

jkff c2 (vdd, vdd, qbar[1], q[2], qbar [2] ) ;

jkff c3 (vdd, vdd, qbar[2], q[3], qbar [3] ) ;

endmodule

```

#### **Component Code**

```

module jkff ( j, k ,clk, qx, qxbar ) ;

input clk , j , k ;

output qx, qxbar ;

reg qx, qxbar ;

initial

begin

qx = 1'b0 ;

qxbar = 1'b1 ;

end

always @ ( posedge clk )

begin

qx = ( j & ( ~ qx ) ) | ( ( ~ k ) & qx ) ;

qxbar = ~ qx ;

end

```

#### endmodule

```

Test Bench :

module sync_test;

reg clk;

wire [3:0] q;wire [3:0] qbar;

async uut (

.clk(clk),

.q(q),.qbar(qbar)

);

initial

clk =1'b0;

always #10 clk=~clk;

endmodule

```

**RESULT:** Verilog code for the asynchronous counter circuit and its test bench for verification is written, the waveform is observed and the code is synthesized with the technological library and is verified

## PART - B ANALOG DESIGN

#### Steps of Execution for schematic :

- 1. Start RedHat OS

- 2. Click on vsmitvlsi

- 3. Password: vlsilab

- 4. Select network connection: system eth0

- 5. Right click and select Open in Terminal

- 6. Write cd enter, source ams.cshrc enter, dmgr\_ic enter

- 7. Click on File --- New --- Project ----

- 8. Project path: /home/vsmitvlsi/inverter

- 9. Library: select: PDK---generic13 ----- enter OK

- 10. Click on add standard library --- click --- OK

- 11. Right click on project--- new --- library ---- library name: inv --- OK

- 12. Right click on library inv --- new --- Schematic ----

- 13. Cell name --- inv --- press OK

- 14. After blank schematic window opens, Add instance

- 15. Generic13/symbols pmos,nmos,resistance,capacitance

- 16. Genericlib --- vdd, vss, ground etc

- 17. Source --- dc, ac, pulse voltage, current sources etc

- 18. Draw Schematic Diagram with appropriate ports

- 19. Click on save & check

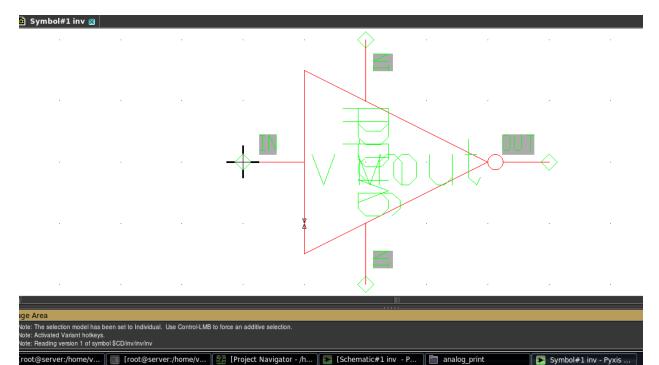

- 20. Add --- generic symbol --- Choose shape

- 21. Customize pinlist --- press OK

- 22. Save & check the generated symbol

- 23. In the project navigator --- right click --- schematic (for test circuit)

- 24. Select the schematic instance

- 25. Draw the test circuit --- Save

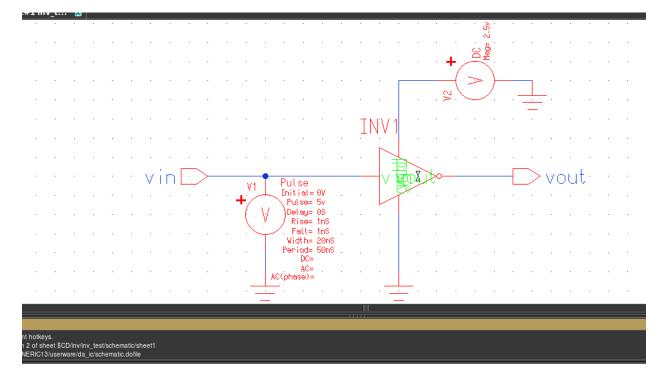

- 26. Enter Simulation mode

- 27. New design configuration

- 28. Name: eldo --- Press OK

- 29. Choose Setup Environment

- 30. Viewer --- select ---- Satrt EZwave Automatically --- Press OK

- 31. Setup simulation --- Analysis --- Transient (give appropriate values)

- 32. Setup simulation --- Analysis --- DC (give appropriate values)

- 33. Setup simulation --- Analysis --- AC (give appropriate values)

- 34. Setup simulation --- libraries Typical

- 35. Setup simulation --- Includes --- unselect include\_all

- 36. Setup simulation forces --- from schematic --- press ctrl & choose input output

- 37. Setup simulation output --- ( Choose inputs and outputs ) Add

- 38. Save --- Run

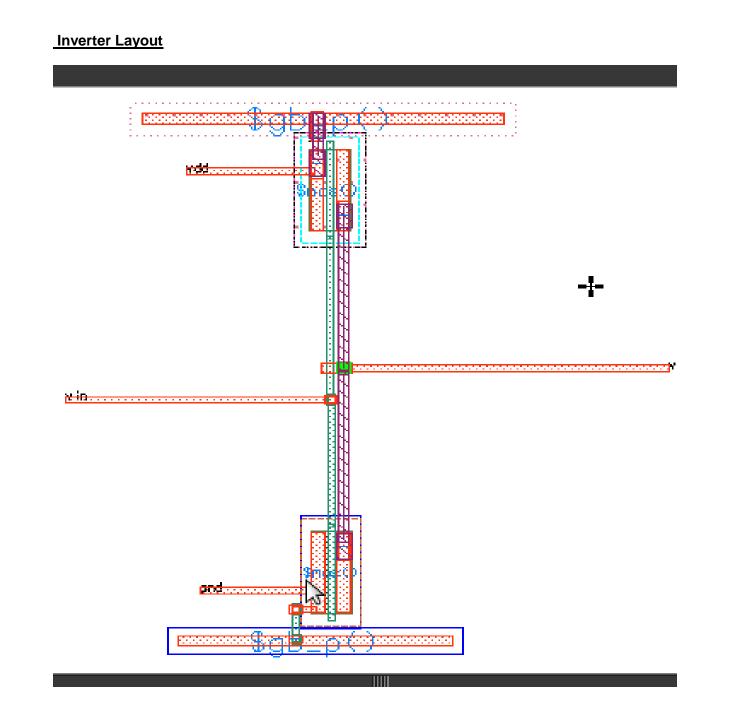

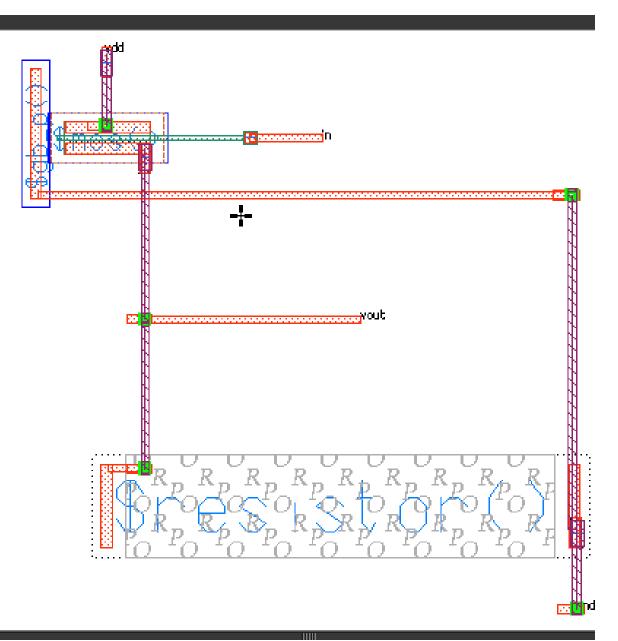

Steps of Execution for Layout:

- In the project navigator --- Select Schematic & in Project Hierarchy right click --new --- layout

- 2. Choose OK to Launch Editor

- 3. Setup toolbar SDL toolbar

- 4. Pick and place component from SDL tollbar

- 5. Pick and place ports from SDL toolbar

- Setup windows object editor add device -- \$gb\_p psub, nwell for nmos, pmos

- 7. IRoute for connectivity using appropriate layers , add --- text on ports M1 OK

- 8. Save the layout

- 9. Tools -- Calibre DRC Run DRC

- 10. Tools Calibre LVS Run LVS

- 11. Tick Mark and Smileys indicates NO LVS Errors

- 12. Tools Calibre PEX input Browse "\*.src.net "-input Netlist

- enable export from schematic Run PEX

## EXPT.NO.1

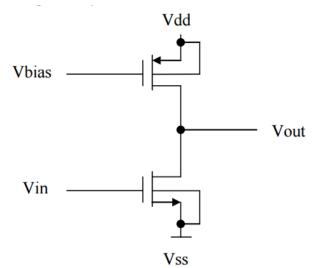

**TITLE :** To simulate the schematic of the CMOS inverter, and then to perform the physical verification for the layout of the same.

#### **TOOL REQUIRED:** Mentorgraphics

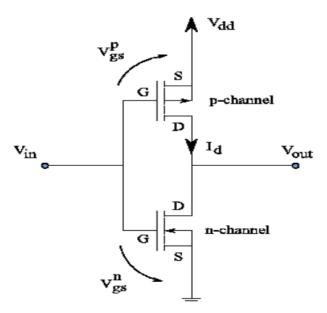

**THEORY:** The inverter is universally accepted as the most basic logic gate doing a Boolean operation on a single input variable. Fig.1 depicts the symbol, truth table and a general structure of a CMOS inverter. As shown, the simple structure consists of a combination of an pMOS transistor at the top and a nMOS transistor at the bottom.

CMOS is also sometimes referred to as complementary-symmetry metal-oxidesemiconductor. The words "complementary-symmetry" refer to the fact that the typical digital design style with CMOS uses complementary and symmetrical pairs of p-type and n-type metal oxide semiconductor field effect transistors (MOSFETs) for logic functions. Two important characteristics of CMOS devices are high noise immunity and low static power consumption. Significant power is only drawn while the transistors in the CMOS device are switching between on and off states. Consequently, CMOS devices do not produce as much waste heat as other forms of logic, for example transistortransistor logic (TTL) or NMOS logic, which uses all nchannel devices without p-channel devices.

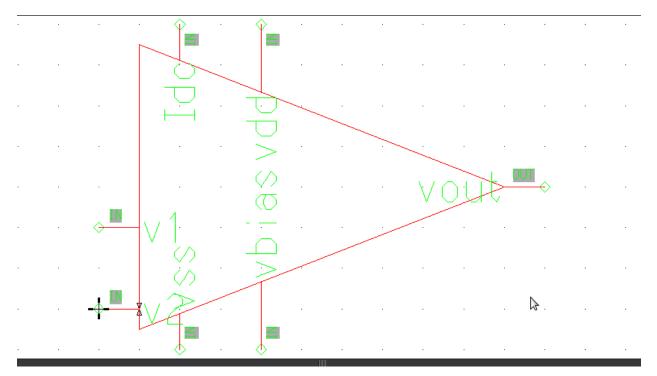

#### Inverter Schematic

|      |   | inv |   |   |   |   |   |  |   |   |   |   |   |    |   |   |   |   |     |               |            | σ               |       |   |   |   |        |    |     |     |   |   |   |   |

|------|---|-----|---|---|---|---|---|--|---|---|---|---|---|----|---|---|---|---|-----|---------------|------------|-----------------|-------|---|---|---|--------|----|-----|-----|---|---|---|---|

|      |   |     |   |   |   |   |   |  |   |   |   |   |   |    |   |   |   |   |     |               |            | Ď               |       |   |   |   |        |    |     |     |   |   |   |   |

|      |   |     |   |   |   |   |   |  |   |   |   |   |   |    |   |   |   |   |     |               |            | í.              |       |   |   |   |        |    |     |     |   |   |   |   |

|      |   |     | · |   |   |   | · |  | · |   | · |   | · | ·  | · |   | · | · |     |               |            | $\bigcirc$      |       | · |   |   | ·      |    |     |     |   |   | · |   |

|      |   |     |   | • |   |   |   |  | • |   |   | • |   |    | • |   |   | • | •   |               | •          | ľ               |       | • | • |   | •      |    |     |     |   |   |   |   |

| • •  | • |     | · | · | • |   | · |  | · |   | • |   | • | •  | · |   | • | · |     |               |            | •               | 1     | • | • |   | ·      | •  |     |     | • |   | · |   |

| • •  | • |     | • | · |   |   | • |  | • |   | • | • | • | •  | • | • | • | • |     | <sup>M1</sup> |            | _¥≘2u<br>L=0.1: |       | • | • |   | •      |    |     |     | • |   | • |   |

| • •  | · | •   | · | · | · | · |   |  |   | N | · |   |   |    | · |   |   |   |     | -q            | ⊢          | NF=1            | sh    | · | · | · |        | ·  |     | ·   | · | · |   |   |

|      | • |     |   |   |   |   |   |  |   | 2 |   |   |   |    |   |   |   |   | pno | ¢.            |            | mt =1           |       |   |   |   |        |    |     |     |   |   |   |   |

|      |   |     |   |   |   |   |   |  |   |   |   |   |   |    |   |   |   |   |     |               | <u>ا</u> . | -               |       |   |   | - | $\geq$ | VC | วยา | t٠  |   |   |   |   |

|      |   |     |   |   |   |   |   |  |   |   |   |   | M | in |   | * |   |   | •   |               |            |                 |       |   |   |   |        |    |     | Ĩ., |   |   |   |   |

|      |   |     |   |   |   |   |   |  |   |   |   |   | , |    |   |   |   |   | 1   | 12            |            | <sub>V⊨2</sub>  |       |   |   |   |        |    |     |     |   |   |   |   |

|      |   |     |   |   |   |   |   |  |   |   |   |   |   |    |   |   |   |   |     |               |            | L=0             | 9.13u |   |   |   |        |    |     |     |   |   |   |   |

|      |   |     |   |   |   |   |   |  |   |   |   |   |   |    |   |   |   |   | nno | ~             |            | NF:             |       |   |   |   |        |    |     |     |   |   |   |   |

|      |   |     |   |   |   |   |   |  |   |   |   |   |   |    |   |   |   |   |     | ~ 1           | -          | •               |       |   |   |   |        |    |     |     |   |   |   |   |

|      |   |     |   | • |   |   | • |  |   |   |   |   |   |    |   |   |   | • |     |               | •          |                 | -     |   |   |   |        |    |     |     |   |   |   |   |

|      |   |     |   |   |   |   | • |  | • |   |   |   |   |    | • |   |   | • | •   |               | •          | $\triangle$     | •     | • | • |   | •      |    |     |     |   |   |   |   |

| • •  | • |     | • | · |   |   | · |  | • |   | • |   | • | •  | · |   | • | • |     | •             | ·          | Ŀ               | •     | · | · | • | •      |    |     |     | • |   | • | • |

| • •  | • |     | • | · |   |   | • |  | • |   | • | • | • | •  | • | • | • | • |     |               | ·          | ק               | •     | • | • |   | •      |    |     |     | • |   | • | • |

| • •  |   | •   |   | • |   | · | · |  |   | ÷ |   |   |   |    |   |   |   | · |     | ÷             |            | Б               | •     | • |   |   |        |    |     | ·   |   | · |   |   |

|      |   |     |   |   |   |   |   |  |   |   |   |   |   |    |   |   |   |   |     |               |            |                 |       |   |   |   |        |    |     |     |   |   |   |   |

| Area |   |     |   |   |   |   |   |  |   |   |   |   |   |    |   |   |   |   |     |               |            |                 |       |   |   |   |        |    |     |     |   |   |   |   |

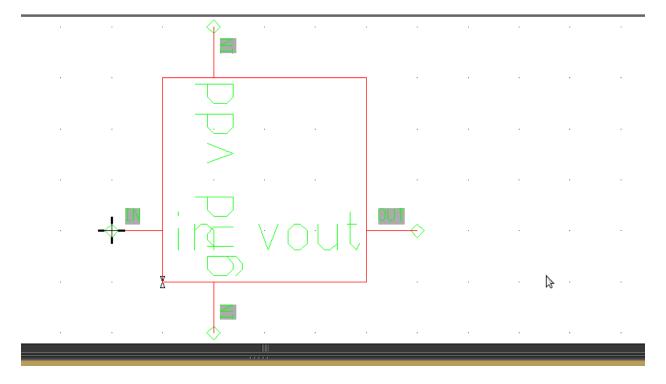

## Inverter Symbol

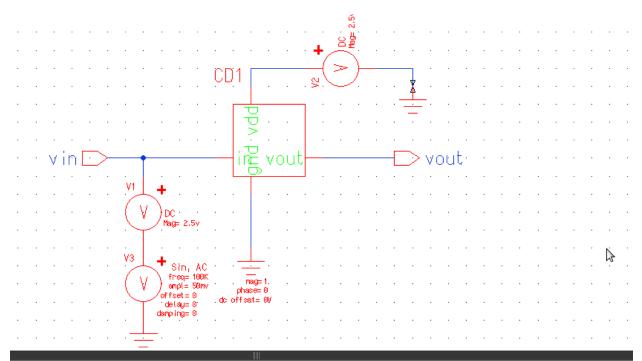

#### **Inverter Test**

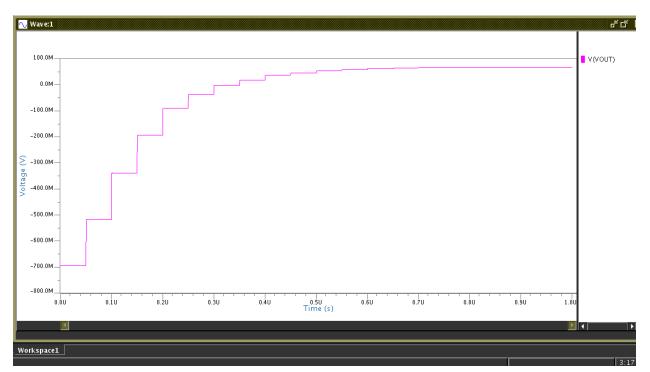

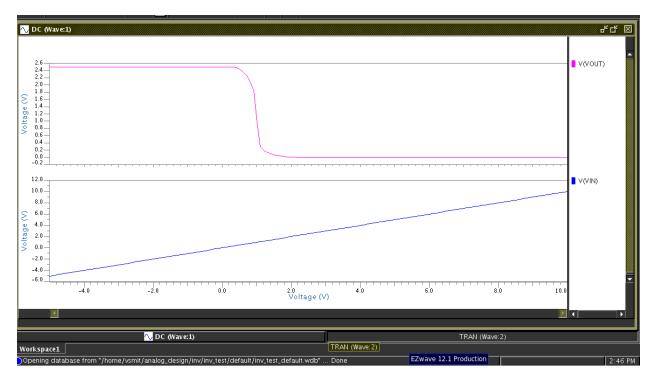

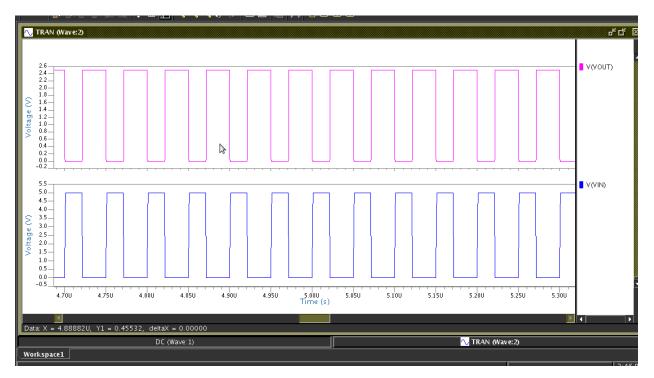

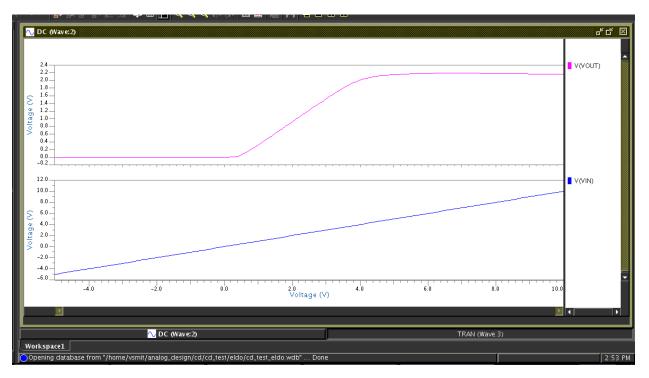

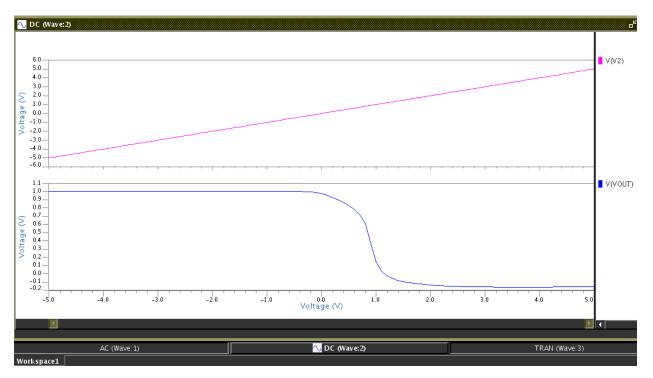

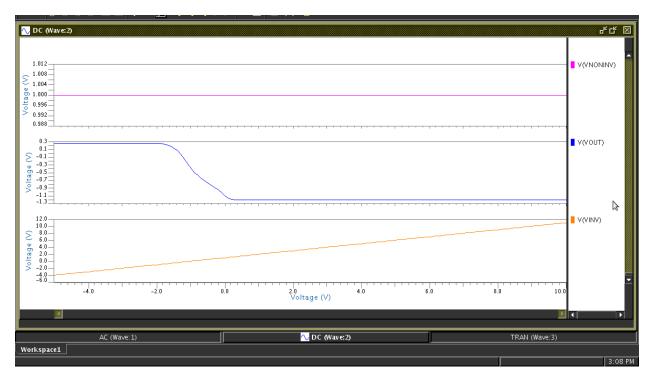

#### **Inverter DCAnalysis**

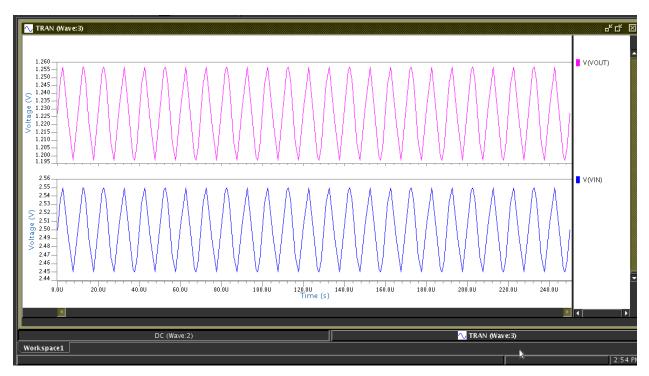

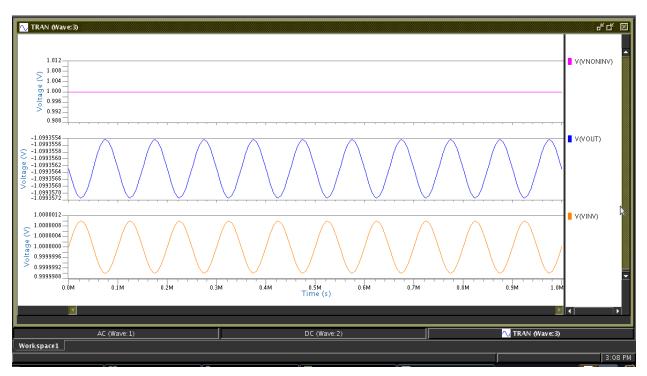

#### **Inverter Transient Analysis**

### Inverter DRC

DEPARTMENT OF ECE

37

| 👸 Applications Places System 📵 🛞 🗹 🔹 🕼                                                                                                                           | Sat Oct 31, 3:21 PM root |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Calibre - RVE v2012.4_25.21 : inv.drc.results                                                                                                                    | _ 🗆 ×                    |

| Ele Vew Highlight Tools Window Setup                                                                                                                             | Help                     |

|                                                                                                                                                                  |                          |

| Show Al 🖶 inv, 32 Results (in 10 of 388 Checks), 32 Waived                                                                                                       |                          |

| G Ag Check / Cat                                                                                                                                                 |                          |

| Check G.1                                                                                                                                                        |                          |

| ✓ Check G.3                                                                                                                                                      |                          |

| Check NW.W.1                                                                                                                                                     |                          |

| ✓ Check NW.W.2                                                                                                                                                   |                          |

| Check NW.S.1                                                                                                                                                     |                          |

| Check NW.S.2                                                                                                                                                     |                          |

| Check NV/S3                                                                                                                                                      |                          |

|                                                                                                                                                                  |                          |

| Check NWA2                                                                                                                                                       |                          |

| Clease MVR.E.1                                                                                                                                                   |                          |

| Check MVR.E.2                                                                                                                                                    |                          |

| Check NWR.C.1                                                                                                                                                    |                          |

| Check NWR C 2                                                                                                                                                    |                          |

| Check NWR.0.1                                                                                                                                                    |                          |

| Check NWR.R.1                                                                                                                                                    |                          |

| Check DNW.11                                                                                                                                                     | ×                        |

| Check DNW.W.1                                                                                                                                                    |                          |

| Check DNW.5.1                                                                                                                                                    |                          |

| Check DNW.E.1                                                                                                                                                    |                          |

| Check DNW.0.1                                                                                                                                                    |                          |

| Check DNW.C.1                                                                                                                                                    |                          |

| 6.1 ( @ Grid must be an integer multiple of 0.005um<br>DRAWN GFORD                                                                                               | ×                        |

|                                                                                                                                                                  |                          |

|                                                                                                                                                                  |                          |

|                                                                                                                                                                  |                          |

|                                                                                                                                                                  |                          |

|                                                                                                                                                                  |                          |

|                                                                                                                                                                  |                          |

| L<br><sup>™</sup> Orbek 6.1                                                                                                                                      | •                        |

|                                                                                                                                                                  |                          |

| Check G1 or Server:/ho ) 📧 [root@server:/ho ] 🛃 Project Navigator ) 🛅 analog_print 🛛 🔯 IC 0: inv > inv (i) ] 🧰 Calibre Interactiv ) 📩 DRC Summary Re ) 💼 Calibre | e - RVE v20 🔲 💼          |

## Inverter LVS

| CAPPlications Places Sys                                       | stem 🙋 🥸 🗹                 |                                        |            |                                       |                        | d) 🚅                      | Sat Oct 31, 3:22 PM | root     |

|----------------------------------------------------------------|----------------------------|----------------------------------------|------------|---------------------------------------|------------------------|---------------------------|---------------------|----------|

|                                                                |                            | Calibre - R                            | VE v2012.4 | 25.21 : svdb inv                      |                        |                           | _ 0                 | ×        |

| <u>Fi</u> le <u>View H</u> ighlight <u>T</u> ools <u>W</u> ind | low <u>S</u> etup          |                                        |            |                                       |                        |                           |                     | Help     |

| 🎾 🖌 🧟 🗍 🕷                                                      | 📡 💱 🔤 Search               | <ul> <li>(*)</li> </ul>                |            |                                       |                        |                           |                     |          |

| + Navigator d" ×                                               | 😃 Comparison Results 🗙     |                                        |            |                                       |                        |                           |                     |          |

| Results                                                        | Layout Cell / Type         | Source Cell                            |            | Nets                                  | Instances              | Ports                     |                     | -        |

| Hy Extraction Results                                          | 🗢 inv 🕀                    | inv                                    |            | 4L, 4S                                | 1L, 18                 | 4L, 4S                    |                     |          |

| Comparison Results                                             |                            |                                        |            |                                       |                        |                           |                     |          |

| 🏇 Parasitics                                                   |                            |                                        |            |                                       |                        |                           |                     | -        |

| ERC<br>ERC Pathchk Polygons Dr                                 | Cell inv Summary (Clean)   |                                        |            |                                       |                        |                           |                     | -        |

| ERC Pathchk Nets Report                                        |                            | SON RESULTS ( TOP LEVEL )              |            |                                       |                        |                           |                     | 14       |

| Reports                                                        |                            |                                        |            |                                       |                        |                           |                     |          |

| Extraction Report                                              | _*                         | ###################################### |            |                                       |                        |                           |                     |          |

| L LVS Report                                                   | ll 1.1                     | CORRECT                                |            |                                       |                        |                           |                     |          |

| Rules                                                          | #                          |                                        |            |                                       |                        |                           |                     |          |

| Rules File                                                     | LRYOUT CELL NAME: inv      |                                        |            |                                       |                        |                           |                     |          |

| View                                                           | SOURCE CELL NAME: inv      |                                        |            |                                       |                        |                           |                     |          |

| M Finder                                                       |                            |                                        |            |                                       |                        |                           |                     |          |

| Schematics                                                     | INITIAL NUMBERS OF OBJECTS |                                        |            |                                       |                        |                           |                     |          |

| D- Layout Netlist lay.net                                      |                            |                                        | _ 🗆 🕫 🗙    | D- Source Netlist inv.calibre.src.net |                        |                           | _ 0 :               | а×       |

| ₽ * ħ, * II *                                                  | * 🗛 🔶 📷                    |                                        |            | ₽ 1 1, 1 1 1 / 1 1                    | * 🚧 < 🛶 🚾              |                           |                     | -        |

| E Subckts                                                      | ୍ର୍ର୍ 🍟 🚽 🖓                | vout vout                              | $\square$  | Subokta                               |                        |                           |                     | $\Delta$ |

| -> mimcap_g13<br>-> spiral inductor lvs                        |                            |                                        |            | - <b>H INV</b>                        | 1 gnd vdd              |                           |                     |          |

|                                                                |                            |                                        |            |                                       |                        | 1                         |                     |          |

|                                                                | i gid                      |                                        |            |                                       |                        | vout vout                 |                     |          |

|                                                                | inv                        |                                        | _          |                                       |                        | 2                         |                     |          |

|                                                                |                            |                                        | _          |                                       |                        |                           |                     |          |

|                                                                | K                          |                                        | 12 M       |                                       |                        |                           |                     | N        |

|                                                                | *                          |                                        |            | 5                                     | * ****                 | a maan waana ku dumaad in |                     |          |

| L                                                              |                            |                                        |            |                                       |                        |                           |                     | •        |

| [root@server:/ho]                                              | [root@server:/ho ] 🛃 Proje | t Navigator 🏾 🛅 analog print           |            | : inv > inv (i) 🔲 Calibre             | Interactiv 🗖 LVS Repor | t File - I                | RVE v20             |          |

## Inverter PEX

| -                                                                   | Calibre Interactive - PEX v2012.4 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21 : inv nev runset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| jie Iranscript                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| ine Treuscubr                                                       | 2etup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>н</u> |

| Rules Jpputa Juputa Qutputs Run Control Trgnorrot Run PEK Start RVE | <pre> EUTYON REDUCTION RECT:<br/> RECTOR FORD FEG:<br/> RECTOR FORD FEG:<br/> RECTOR FORD FEG:<br/> RECTOR FOR FIG:<br/> RECTOR FOR FIG:<br/> RECTOR FOR FIG:<br/> RECTOR FOR FIG:<br/> RECTOR CONTROL CONFLIC: CVTTHE = 0 FEAL THE = 0 FAREAP = 137/138/139 MALLOC = 211/211/211<br/> TO RECTOR FORD.:<br/> RECTOR RECTOR CONFLIC: CVTTHE = 0 FEAL THE = 0 FAREAP = 137/138/139 MALLOC = 211/211/211<br/> RECTOR RECTOR CONFLICT: CVTTHE = 0 FEAL THE = 0 FAREAP = 10<br/> RECTOR RECTOR CONFLICT: CVTTHE = 0 FEAL THE = 0 FAREAP = 10<br/> RECTOR RECTOR FORD = 10<br/></pre> | PEX Natilist File - inv.pex.natilist  Pie Edit Options Windows  * [psyr 1.5 * psychos works - sold - |          |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

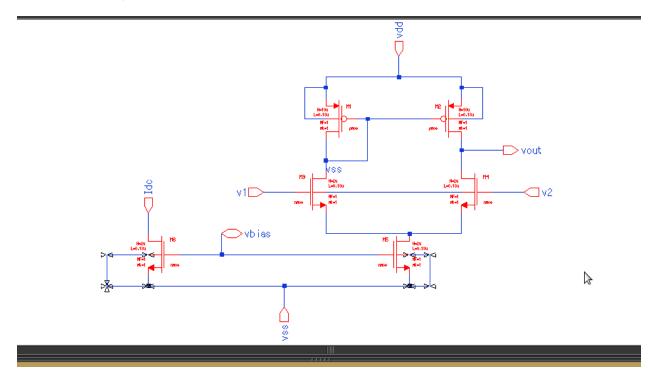

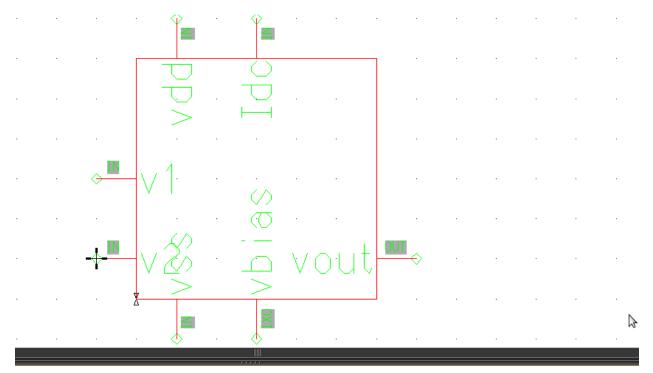

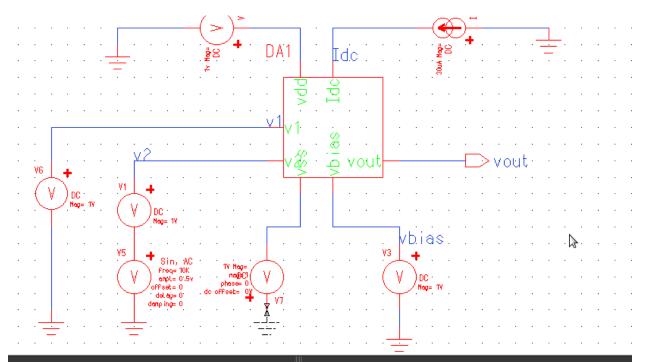

# EXPT.NO. 2 a

**TITLE :** To simulate the schematic of the CMOS common aource amplifier, and then to perform the physical verification for the layout of the same.

#### **TOOL REQUIRED:** Mentorgraphics

**THEORY:** In electronics, a common-source amplifier is one of three basic single-stage fieldeffect transistor (FET) amplifier topologies, typically used as a voltage or transconductance amplifier. The easiest way to tell if a FET is common source, common drain, orcommon gate is to examine where the signal enters and leaves. The remaining terminal is what is known as "common". In this example, the signal enters the gate, and exits the drain. The only terminal remaining is the source. This is a common-source FET circuit. The analogous bipolar junction transistor circuit is the common-emitter amplifier. The common-source (CS) amplifier may be viewed as a transconductance amplifier or as a voltage amplifier. (See classification of amplifiers). As a transconductance amplifier, the input voltage is seen as modulating the current going to the load. As a voltage amplifier, input voltage modulates the amount of current flowing through the FET, changing the voltage across the output resistance according to Ohm's law. However, the FET device's output resistance typically is not high enough for a reasonable transconductance amplifier (ideally infinite), nor low enough for a decent voltage amplifier (ideally zero). Another major drawback is the amplifier's limited high-frequency response.

Common drain amplifier is a source follower or buffer amplifier circuit using a MOSFET. The output is simply equal to the input minus about 2.2V. The advantage of this circuit is that the MOSFET can provide current and power gain; the MOSFET draws no current from the input. It provides low output impedance to any circuit using the output of the follower, meaning that the output will not drop under load. Its output impedance is not as low as that of an emitter follower

using a bipolar transistor (as you can verify by connecting a resistor from the output to -15V), but it has the advantage that the input impedance is infinite. The MOSFET is in saturation, so the current across it is determined by the gatesource voltage. Since a current source keeps the current constant, the gate-source voltage is also constant.

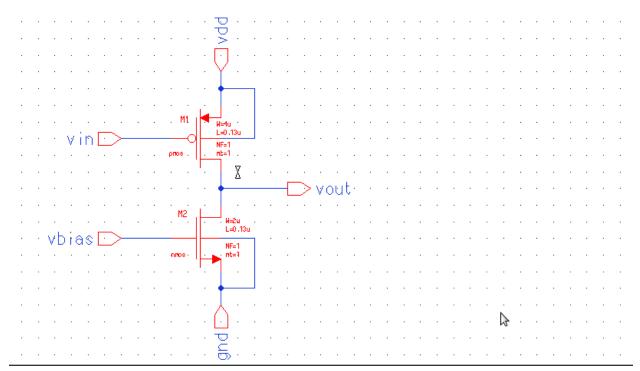

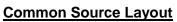

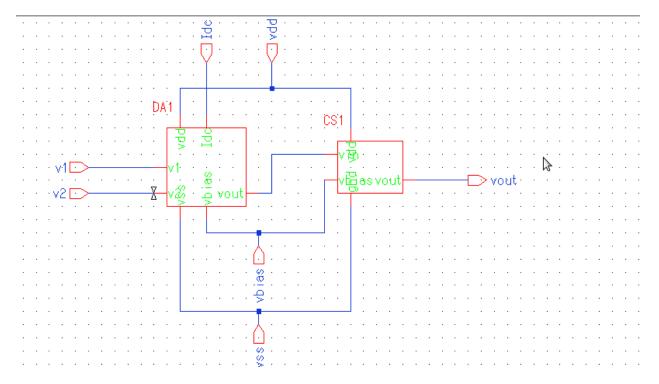

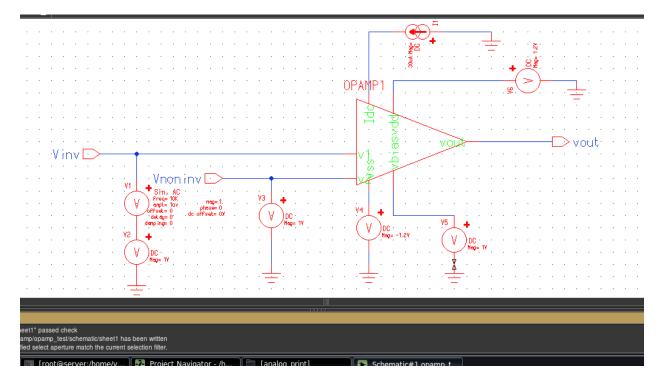

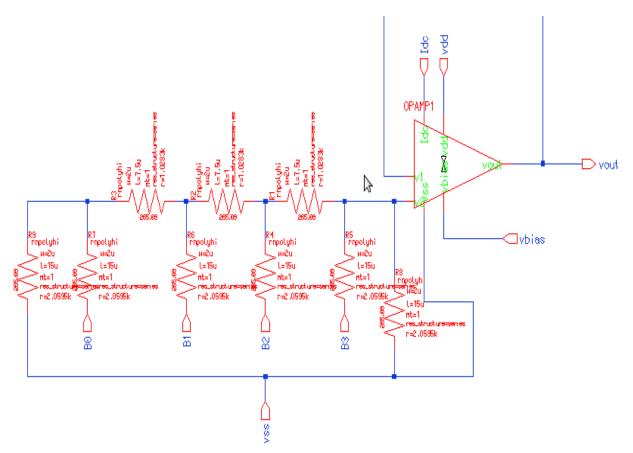

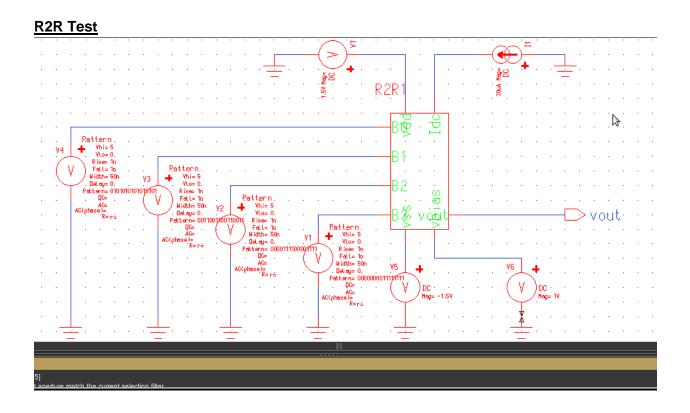

### **Common Source Schematic**

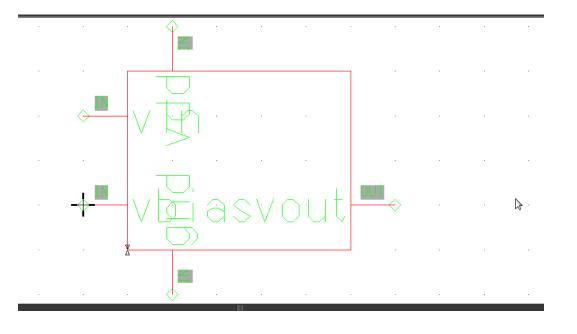

### **Common Source Symbol**

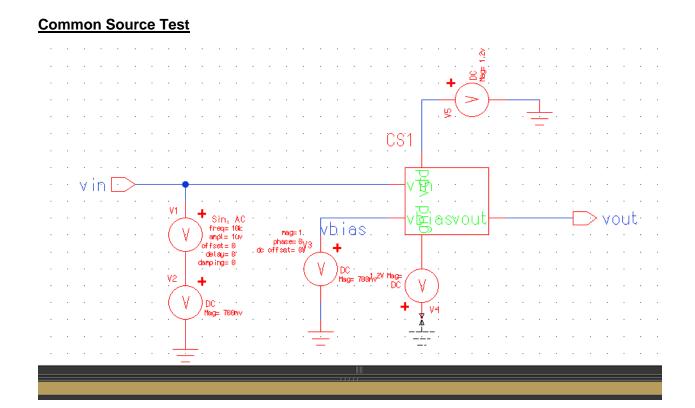

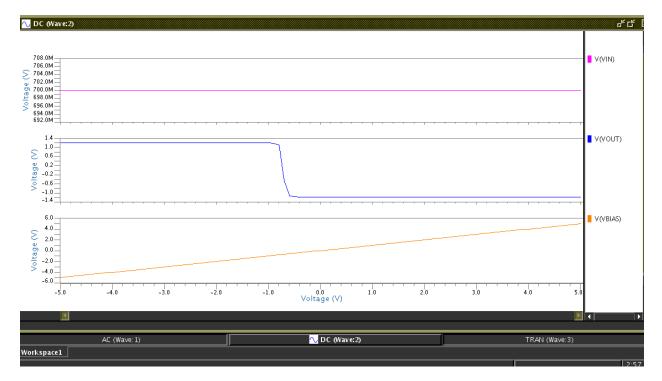

## **Common Source DC Analysis**

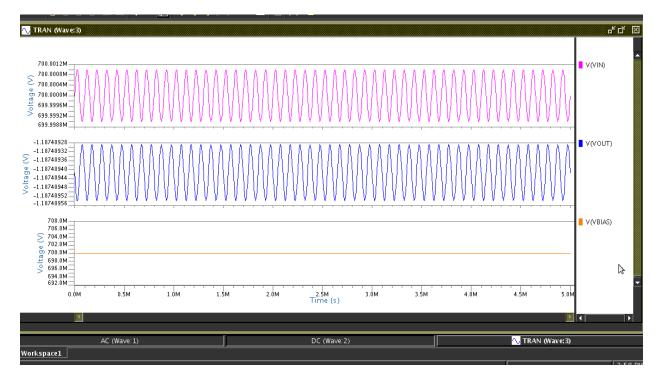

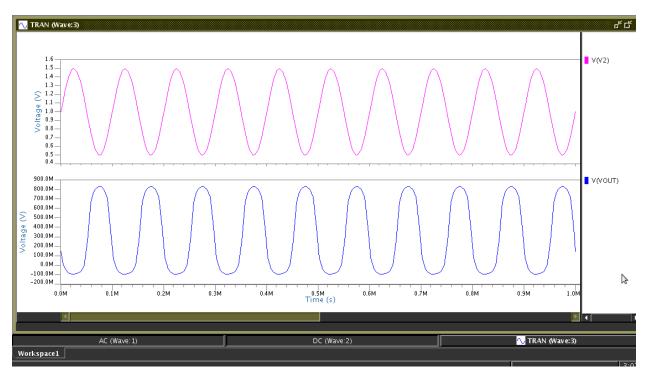

#### **Common Source Transient Analysis**

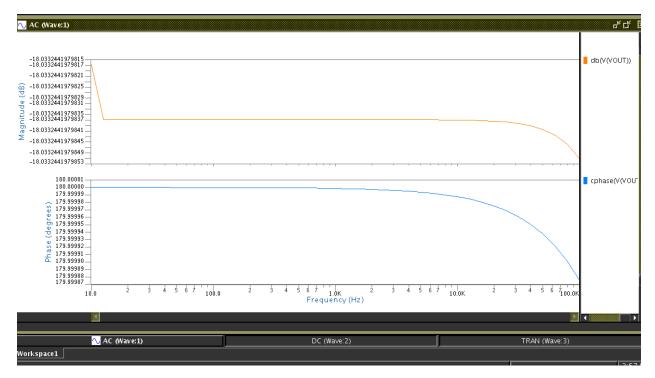

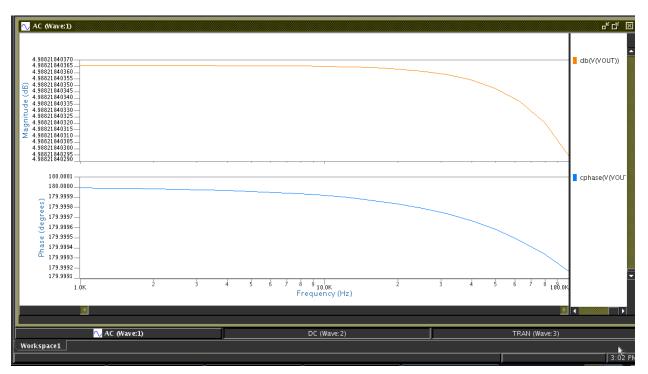

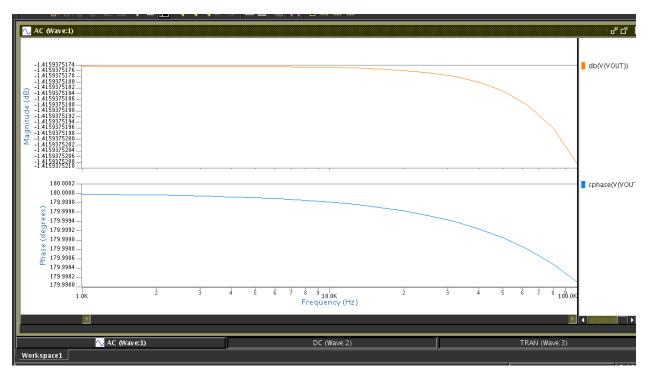

### **Common Source AC Analysis**

# Common Source DRC

| 🕻 Applications Places System ຢ 🎕 롣                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>4</b> > <b>E</b> | Sat Oct 31, 3:37 PM                                       | root   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------|--------|